# Arbeitsblatt 7 / Worksheet 7 Zeitablaufdiagramm / Time flowchart Mechatronik/Mechatronics 3. Ausbildungsjahr / 3<sup>rd</sup> year of training

### **PAIR WORK**

### **PARTNER A**

a) Read the definition. Then tell your neighbour in German what sequential logic is.

In digital circuit theory, sequential logic is a type of logic circuit whose output depends not only on the present input but also on the history of the input. Sequential logic has storage (memory).

Sequential logic is used to construct some types of computer memory, other types of delay and storage elements.

Adapted from http://en.wikipedia.org/wiki/Sequential\_logic, accessed 23/09/2010

| Vocabulary help     |                             |  |

|---------------------|-----------------------------|--|

| sequential logic    | Speicherschaltungen         |  |

| combinatorial logic | logische Grundverknüpfungen |  |

| delay               | Verzögerung                 |  |

## **PARTNER B**

a) Read the definition. Then tell your neighbour in German what combinatorial logic is.

In digital circuit theory, the output of combinatorial logic is a function the present input. Combinatorial logic does not have storage (memory).

Most practical computer circuits are a mixture of combinatorial and sequential logic.

Adapted from http://en.wikipedia.org/wiki/Sequential\_logic, accessed 23/09/2010

| Vocabulary help     |                             |  |

|---------------------|-----------------------------|--|

| combinatorial logic | logische Grundverknüpfungen |  |

| sequential logic    | Speicherschaltungen         |  |

b) Now work together with your partner to explain the difference between combinatorial logic and sequential logic.

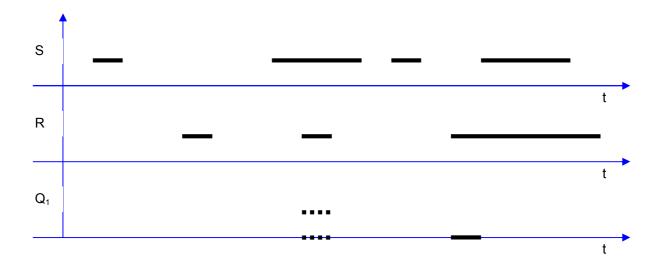

|        | Truth t | table | RS Flipflop / SR latch                   |

|--------|---------|-------|------------------------------------------|

|        | R       | S     | Q1                                       |

| Step 1 | 0       | 0     | like before                              |

| Step 2 | 0       | 1     | "1" is set                               |

| Step 3 | 0       | 0     | "1" as before - Situation known          |

| Step 4 | 1       | 0     | "0" is set                               |

| Step 5 | 0       | 0     | "0" as before, Situation known           |

| Step 6 | 1       | 1     | not allowed                              |

|        | 1       | 1     | "0" if R is made dominant dominant reset |

|        | 1       | 1     | "1" if S is made dominant dominant set   |

A time flowchart is used to investigate sequential logic or combinatorial logic.

# c) Complete the time flowchart whereas R=1 and S=1 means an unknown situation